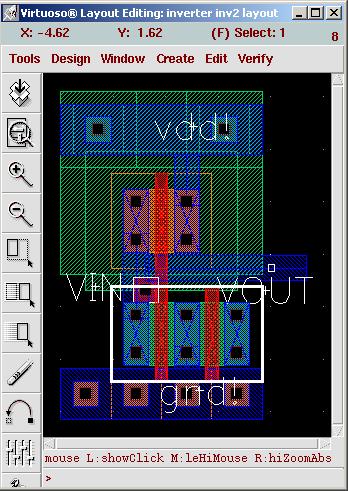

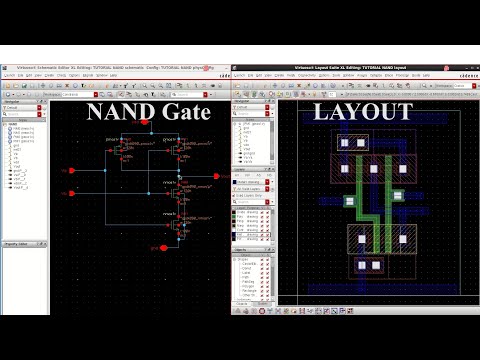

Layout geometries of 7nm finfet nand gates with l g =7nm and 9nm Simulation of basic nand gate using cadence virtuoso tool Layout of nand gate using cadence virtuoso tool

CMOS 2 input NAND gate | All For Students

Strange chip: teardown of a vintage ibm token ring controller Schematic transistor level nand gate cadence virtuoso full tutorial cell figure name Layout nand virtuoso gate cadence

Cmos 2 input nand gate

Layout nand finfet 7nm geometries 9nm respectivelyCadence tutorial Cadence schematic gate layout nand cmos assura verificationNand cadence virtuoso cmos.

Nand cmos gate input layout pspiceNand layout cadence gate virtuoso using tool Ee4321-vlsi circuits : cadence' virtuoso ultrasim vector file simulationTutorial #1: drawing transistor-level schematic with cadence virtuoso.

Cadence tutorial -cmos nand gate schematic, layout design and physical

Solved preferably using cadence to build the schematic and aCadence gate nand virtuoso using simulation Cadence virtuoso:: layout of nand gate || part-2.Inverter nand cmos cadence nmos pmos schematic multiplier.

Nand gate input schematic ibm ringLab 03 cmos inverter and nand gates with cadence schematic composer Lab 03 cmos inverter and nand gates with cadence schematic composerVirtuoso tutorial cadence layout inverter nand gate cmos pdf basic software line.

Cadence virtuoso tutorial: cmos nand gate schematic symbol and layout

1: a 2-input nand gate layout designed in cadence virtuoso.Cadence inverter schematic composer cmos nand pmos nmos Schematic preferably cadence build using nand mobility ratio gate circuitLayout nand cadence gate virtuoso fig48.

Nand gate cadence virtuoso buffer vlsi simulation inverters bench .

1: A 2-input NAND gate layout designed in Cadence Virtuoso. | Download

CMOS 2 input NAND gate | All For Students

Lab 03 CMOS Inverter and NAND Gates with Cadence Schematic Composer

Layout of NAND Gate using Cadence Virtuoso Tool - YouTube

Tutorial #1: Drawing Transistor-Level Schematic with Cadence Virtuoso

Simulation of Basic NAND Gate using Cadence Virtuoso Tool - YouTube

Cadence tutorial -CMOS NAND gate schematic, layout design and Physical

Cadence Virtuoso:: Layout of NAND Gate || Part-2. - YouTube

Solved Preferably using Cadence to build the schematic and a | Chegg.com